Acharya Nagarjuna University (ANU) 2005 B.Tech Electronics and computers EM 314 VHDL - Question Paper

III/IV B.Tech Degree exam

October 2005

VHDL

EM 314

m .V'JJfEV . '

' (EM 314)

afr': -J'.: '

III/TV B.Tech. DEGREE EXAMINATION, OCTOBER 2005.

First Semester VHDL

Time : Three hours Maximum: 70 marks

Answer Question No.l compulsorily. (7x2 = 14)

Answer ONE question from each Unit. (4 x 14 = 56}

All questions carry equal marks.

(aj What ia a typical design flow for designing VLSI IC circuits?

1.

(b) Difference between top - down and bottom - up design methodologies for digital design.

(e) What are the logic value set and data types such as any nets, registers and numbers?

(d) Explain the port connection rules in a module instantiation.

Ce) What are fall and tumoff delays in tJui gatelervel design?

(f) Enumerate the continuous assignments (assign) statement and restriction? on the assign statement.

(g) Give the significance of structured procedures always and initial in behavioral modeling.

UNIT I

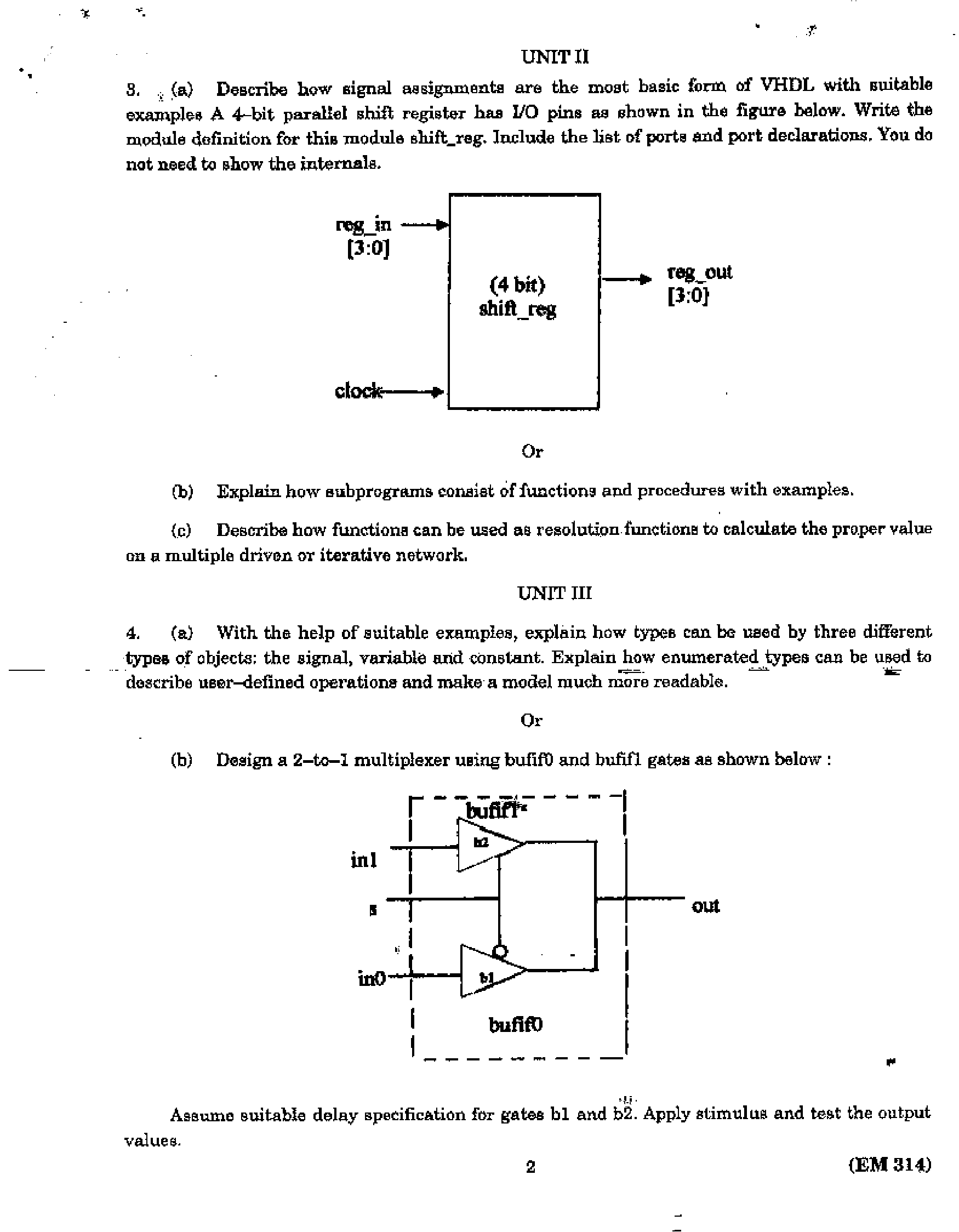

(a) Explain the following basic VHDL building blocks :

2.

(i) Entity tii) Architecture

(iii) Configuration

(iv) Driver.

Or

(b) Write the following variables in VHDL.

(i) An 8-bit vector net called a_in.

(ii) A 32bit storage register called address. Bit 31 must be the most nigwifiMmi-. bit. Set the value of the register to a 32-bit decimal number equal to 3.

(iii) A tame variable called snapjhot.

(iv) A memory MEM containing 256 words of 64 bits each.

5, (a) A full subtracter has three 1-bit inputs x,y and % (previous borrow) and two 1-bit outputs D(di Serenes) and B(borrow). The logic equations for D and B are as follows :

D = x'c/'z + *}''*' + x.y.f ::i

B +x'.2 +y.z

Write the Ml VHDL description for the full subtracter module, including I/O porta (Remember that + in logic equations corresponds to a logical & operator in dataflow). Instantiate the subtracter inside a stimulus block and teat all eight possible combinations of 2, y antz given in the following truth table.

|

X |

Y |

z |

B |

D |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

Or |

(b) Design, a negative edge-triggered D-flip-flop (D_FF) with synchronous clear, active high DJFF clears only at a negative edge of clock when dear is high). Use behavioral statements only. (Hint: Output q of D_FF must be declared as Teg). Design a clock with a period of 10 units and test the D-FF,

|

Attachment: |

| Earning: Approval pending. |