Maharashtra State Board of Technical Education 2008 Diploma Computer Engineering Digital Techniques - Question Paper

Sample Question Paper - I

- Computer Engineering Group

Course Name Course code Semester Subject Duration

- CO/CM/CD/IF

- Third

- Digital Techniques

- 3 hours

Marks: 80

1. All questions are compulsory.

Instructions:

2. Figures to the right indicates full marks.

3. Use of non-programmable calculator is permissible.

Q 1: Attempt any Eight of the following:

(8 x 2 = 16)

a) Define Fan-out & Noise margin.

b) Represent timing diagram of digital signal for positive & negative logic in TTL.

c) Compare TTL & CMOS logic families(any four points).

d) Draw logic symbol & truth-table for EX-OR gate.

e) Simplify using Boolean algebra-

A.B + A.B + A.B

f) Draw block diagram of 4:1 MUX and give its truth table.

g) Draw Full Adder using two Half adders.

h) Draw neat diagram of clocked S-R flip-flop & write its truth-table.

i) Differentiate between static & dynamic RAM

j) Give the classification of different types of semiconductor memories.

Q 2: Attempt any Three of the following: (4 x 3 = 12)

a) Draw circuit for i) AND using NOR ii) OR using NAND.

b) State & prove De Morgan's Theorems.

c) Prove using De Morgan's Theorem -

i) (A + B) + (C+ D) = (A + B) (C+ D)

ii) A.B + C.D = AB . CD

d) Realize the following Boolean expression using basic gates.

i) Y = (A + C) (B+ C)

ii) Y = A.B + B. C

Q 3: Attempt any Three of the following: (4 x 3 = 12)

a) Draw 9-bit odd parity generator using IC 74180.

b) Draw & explain half subtractor.

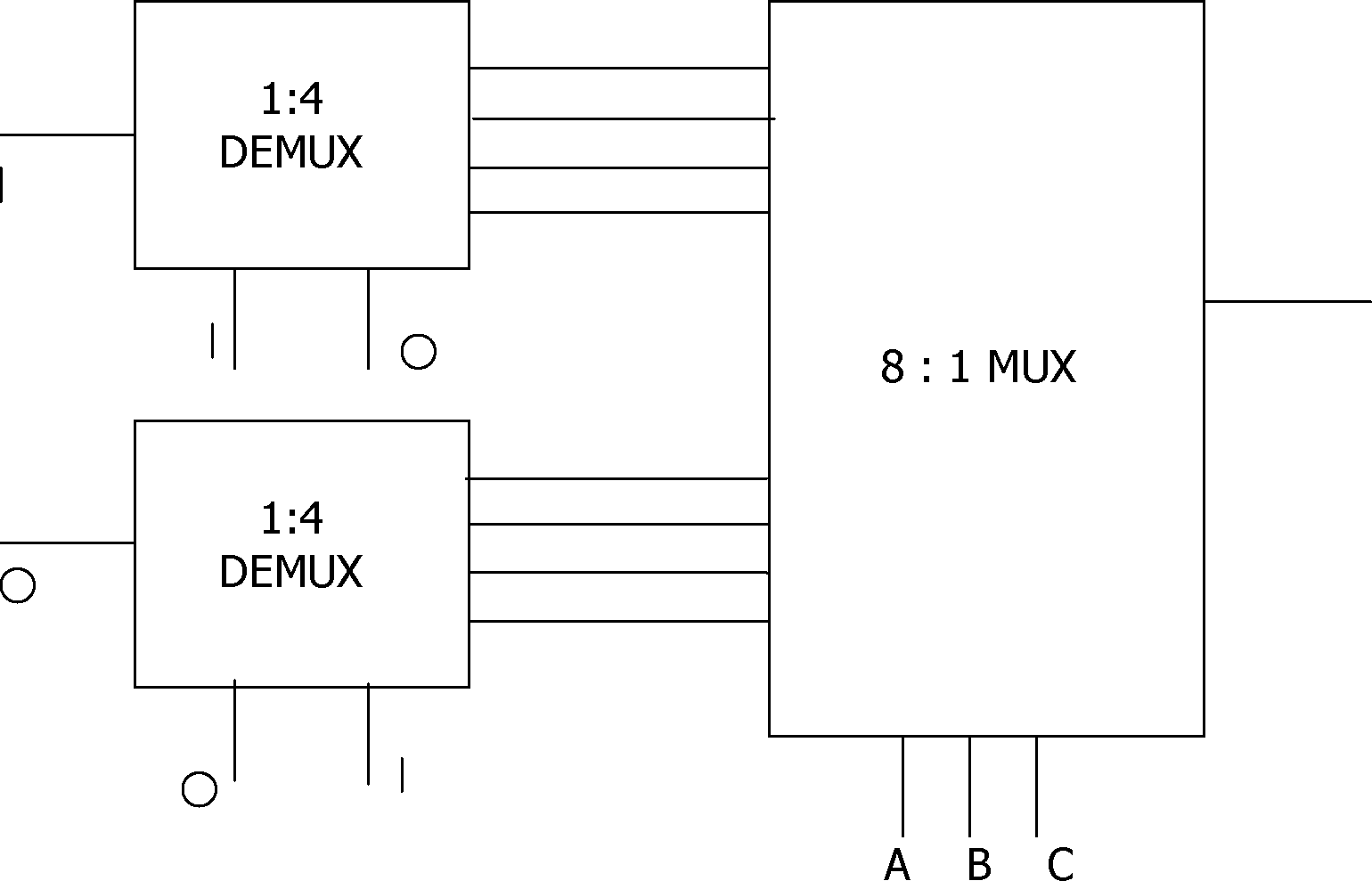

c) Implement the following function using 8:1 MUX.

Y = Zm (0, 2, 3, 6).

d) Implement following expression using NAND gates only.

Y = A.B + B.C + C.A

Q 4: Attempt any Four of the following: (4 x 4 = 16)

a) Describe the function of 4-bit SISO shift register with the help of block diagram , truth-table, timing diagram.

b) State four applications of counters.

c) What is race around condition? How it can be avoided?

d) Compare RAM & ROM.

e) Design Asynchronous MOD-10 Counter.

f) Draw neat diagram of R/2R ladder type DAC. Find its output expression.

Q 5: Attempt any Three of the following: (4 x 3 = 12)

a) List advantages & disadvantages of Ramp type ADC.

b) Draw block diagram of Digital Comparator IC 7485 & write its function table.

c) Describe four specifications of DAC.

d) An 8-bit converter is driven by 500 KHz clock. Find -

i) Maximum conversion time

ii) Average conversion time.

Q 6: Attempt any Three of the following: (4 x 3 = 12)

a) Determine 8:1 MUX output as select inputs A,B,C change from 000 to 111.

b) Describe edge triggering & level triggering with respect to flip-flop.

c) An 8 MHz square wave clocks a 5-bit ripple counter. What will be the frequency at output of last flip-flop & the duty cycle of this counter.

d) Differentiate Synchronous & Asynchronous Counter (any four points).

3

|

Attachment: |

| Earning: Approval pending. |