Bengal Engineering and Science University 2006 B.E Computer Science and Engineering Digital System Design & Implementation - Question Paper

the ques. paper is with the attachment.

Bx/BESUS/ CST-803/ 5/ 06

B.E. (CST) Part-IV 8th Semester Examination, 2006

Digital System Design & Implementation

Time : 3 hours Full Marks : 100

Answer any FIVE questions.

A

1.

A

3

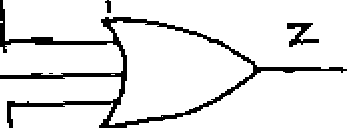

Fig.-l

a) Find the set of all tests that detect the fault a s-a-0.

b) Find the set of all tests that detect the fault b-s-a-(

c) Find the set of all tests that detect the multiple fault {a s-a-0, b s-a-0}

d) Find a circuit that has an undetectable stuck fault. [5+5+5+5|

a) Mention the major advantages of PLA design.

b) Find minimal cost of PLA design using column folding and block folding technique of following functions,

F, = B + CE + ADE F2 = AD + BC

c) What is shrinkage fault and appearance fault of PLA? 14+12+4]

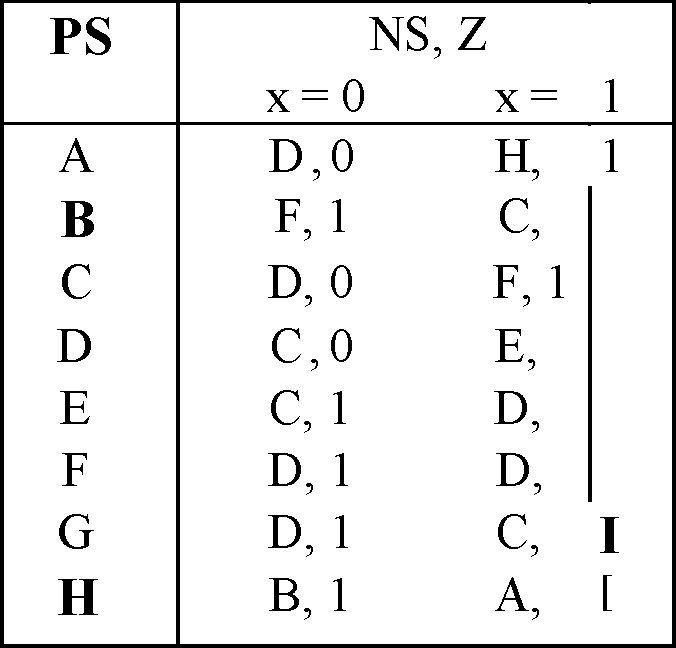

Table-1

a) Find the equivalence partition for the machine shown in Table-1.

b) Find a minimum length sequence that distinguishes state A from state B.

c) Find minimal form of above machine.

d) Explain redundancy with circuit diagram. |6+6+4+4]

4. a) What are the differences between Ad-hoe approach and structured approach of Design for testability?

b) What are the advantages and disadvantages of LSSD method?

c) What are the differences between scan path approach & LSSD approach? Explain with circuit diagram. [4+7+9]

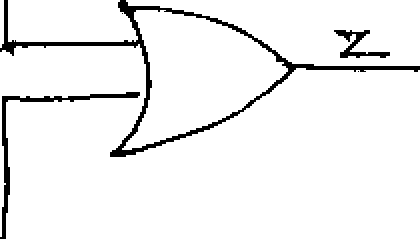

C

a) Find the set of all tests that detect fault a s-a-0.

b) Find the set of all tests that detect multiple faults (c s-a-1, a s-a-0).

c) Find a counter example to the following statement:

"In a combinational circuit two fault f and g are functionally equivalent iff they are always detected by the same test". [4+6+10]

6. a) What are the advantages of Random Access scan approach in comparison to

LSSD approach of DFT?

b) Explain different modes, of BILBO register with block diagram of 8 bit BILBO register.

c) Explain growth fault and disappearance fault of PLA. |5+lO+5|

7. a) Explain stuck-open fault of CMOS circuit with diagram.

b) What are the different stages of VHDL architecture?

c) Explain Signature Analysis method of DFT with Block diagram. [5+7+8]

|

Attachment: |

| Earning: Approval pending. |